Visual Designer of Experiments on Parallel Accelerators

Intended Scope: Master thesis or software project

Required Skills: C/C++, C#, GUI, visualization, and overall knowledge about parallel programming and compilers

Description:

Current parallel accelerators such as GPGPUs or Xeon Phi devices usually employ offload computational model -- i.e., the most computationally intensive parts are offloaded to the accelerator while the CPU is free to perform other tasks. When a new parallel algorithm is being developed and tested, nearly 90% of its prototype implementation code is similar to previous projects. These parts of code, which can be easily deferred into libraries or templates, comprise functionality like:

- generating random data or loading data from files

- device detection and initialization

- copying/mapping input data to the device

- retrieving and verifying the results

- measuring the performance

- performing basic testing to determine optimal configuration constants (e.g., thread block size in CUDA)

Implementing this functionality over and over with each new experiment is quite tedious and error prone. This project should yield an experimental platform, which is expected to simplify design of parallel experiments that employ offload model.

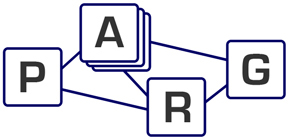

The application will provide a visual interface for designing a kernel execution pipeline and data transfers. Regular parameters of the experiment, such as data sources, buffer structures, etc. will be configurable via visual GUI. The source code of the kernels will be edited in a text form. The application will generate a C/C++ code which will be compiled by external compilers. The application will also be able to execute the compiled experiment either locally, or remotely (via SSH) and gather/parse the experimental results.

This project could be either implemented as a Software Project or as multiple Master theses. In the first phase, it should support either OpenCL or CUDA framework, but the ultimate goal is to support CUDA, OpenCL, and Xeon Phi devices (using explicit offload model).

Note: Lecture NPRG058 "Advanced Programming in Parallel Environment" covers most of the technical details required for this project.